ICP刻蚀介质层及参数调控

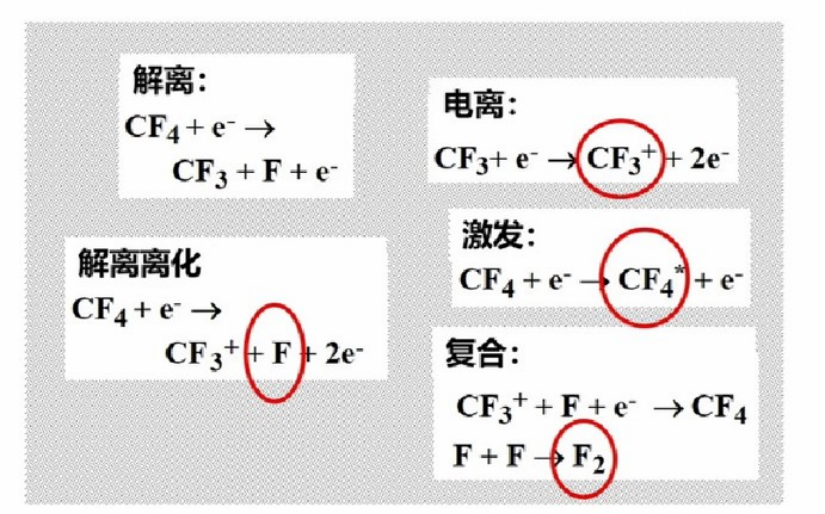

了解介质层干法刻蚀,首先需要了解用于刻蚀等离子体的产生过程,以氧化硅为例,等离子体产生过程如下:首先,在射频电极的作用下,CF4气体经历一系列步骤,包括解离、电离、离化、激发和复合(见图2)。在这个过程中,CF4气体被分解为离子(正电、负电)、电子和氟自由基,它们相互反应形成原子或分子。同时,这些反应在刻蚀腔内形成了辉光区,即我们通常在刻蚀腔中观察到的明亮区域。

图1

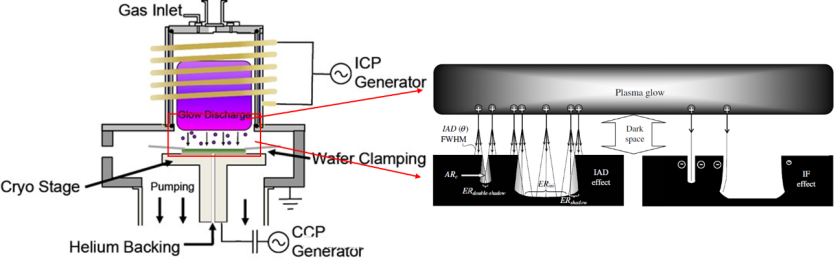

然而,由于电子的运动速度远远高于离子,会在wafer和辉光区之间形成自发产生的电势差(称为暗区)。具体而言,Wafer区的电势较低,而辉光区的电势较高。受到这种自发产生的电压的影响,离子会自发地轰击衬底,而这种轰击的能量与辉光区的等离子体浓度密切相关。通常情况下,等离子体浓度越大,自发产生的电压越大,因此离子轰击的能量也越强。

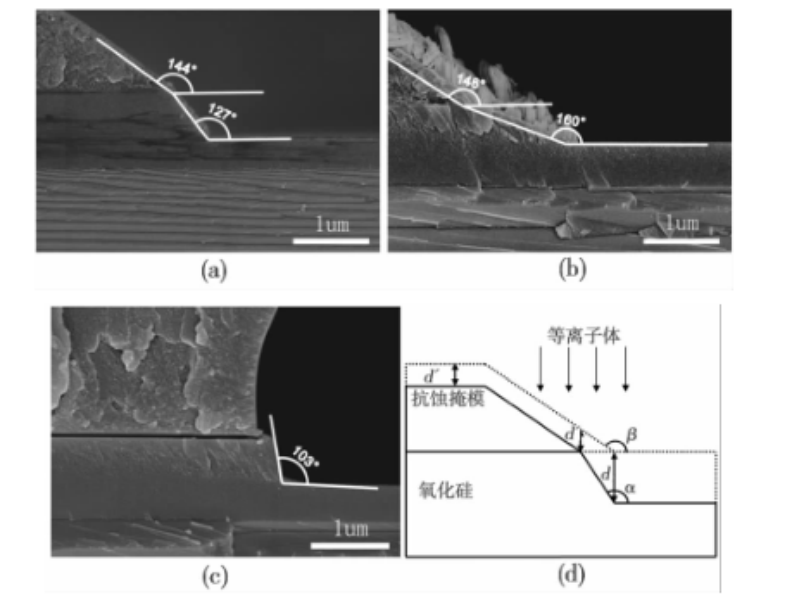

针对氧化硅刻蚀,主要评估指标包括侧壁形貌和粗糙度。图3展示了使用不同掩膜进行氧化硅刻蚀后的侧壁形貌。其中,a采用正性光刻胶作为掩膜,CF4作为刻蚀气体,刻蚀后的角度小于光刻胶的角度。b采用正性光刻胶作为掩膜,CF4+O2作为刻蚀气体,刻蚀后氧化硅角度大于光刻胶,这是由于氧气的引入导致光刻胶变性以及刻蚀选择比的降低。c采用负性光刻胶,CF4作为刻蚀气体,可以看到氧化硅侧壁更趋向于90°。因此,对比得知,侧壁角度随刻蚀选择比的减小而增大。这一系列实验结果表明,在氧化硅刻蚀过程中,选择合适的掩膜和刻蚀气体组合对于侧壁形貌至关重要。氧化硅刻蚀的选择比变化会直接影响侧壁的形状,需要在侧壁角度和材料选择比之间取得平衡[1]。

图3

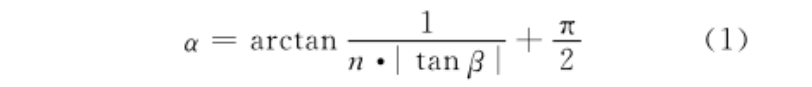

针对于此,研究人员通过计算给出了选择比和刻蚀角度的计算公式,如图3d和图4所示。图中α为二氧化硅的侧壁角度,β为抗蚀掩模的侧壁角度,d 为二氧化硅被刻蚀的深度,d'为抗蚀掩模被刻蚀的深度,若以 n 表示选择比,则 d'=d/n。

根据芯云的了解,提高选择比可以通过以下两个方向进行:

1)选择金属作为刻蚀掩膜,例如铝、铬、镍等。

2)由于一般氧化硅的刻蚀速率在达到一定平台后趋于稳定,因此可以通过优化氧化硅和掩膜的刻蚀速率平衡来增加选择比。

调节刻蚀粗糙度可以通过以下几个方向进行:

1)射频功率和气体流量:适当的射频功率和气体流量可以影响等离子体的密度和能量,从而调整刻蚀速率和表面质量。不适当的功率和流量可能导致表面粗糙度问题。

2)工作压力:控制腔体压力对于实现均匀的刻蚀表面至关重要。过高或过低的工作压力可能导致不均匀的刻蚀表面。

3)表面处理:在刻蚀之前,确保样品表面准备工作得当。保持干净、平整的初始表面有助于获得更好的刻蚀效果。

4)温度控制:在刻蚀过程中合理控制温度,避免过高的温度可能引起材料结构变化,导致表面粗糙度。在某些情况下,降低刻蚀温度可能有助于改善表面质量。

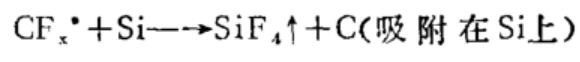

此外,在硅上氧化硅刻蚀的过程中需要特别注意过刻蚀的问题。如下反应方程所示,过刻蚀可能在硅表面留下碳层,不仅会对后续工艺产生影响,甚至可能影响器件的性能。因此,对于硅上氧化硅刻蚀,需要谨慎处理过刻蚀,以确保获得高质量的刻蚀表面。

[1]: 杜文涛,曾志刚,胡志宇.氧化硅RIE刻蚀工艺研究[J]; 半导体光电,2014, 35(2),57-60.DOI: 10.16818/j.issn1001-5868.2014.01.015

服务热线:

服务热线: